# CWDSP1650 DSP Core

# **Technical Manual**

January 1998

Order Number C14049

Document DB14-000071-00, First Edition (January 1998) This document describes revision A of LSI Logic Corporation's CWDSP1650 DSP Core Technical Manual and will remain the official reference source for all revisions/releases of this product until rescinded by an update.

## To receive product literature, call us at 1.800.574.4286 (U.S. and Canada); +32.11.300.531 (Europe); 408.433.7700 (outside U.S., Canada, and Europe) and ask for Department JDS; or visit us at http://www.lsilogic.com.

LSI Logic Corporation reserves the right to make changes to any products herein at any time without notice. LSI Logic does not assume any responsibility or liability arising out of the application or use of any product described herein, except as expressly agreed to in writing by LSI Logic; nor does the purchase or use of a product from LSI Logic convey a license under any patent rights, copyrights, trademark rights, or any other of the intellectual property rights of LSI Logic or third parties.

Copyright © 1997, 1998 by LSI Logic Corporation. All rights reserved.

#### TRADEMARK ACKNOWLEDGMENT

LSI Logic logo design and CoreWare are registered trademarks and MiniRISC, GigaBlaze, G10, and Right-First-Time are trademarks of LSI Logic Corporation. PineDSPCore and OakDSPCore are registered trademarks of the DSP Group. All other brand and product names may be trademarks of their respective companies.

### Contents

| Preface   |       |           |                                         |      |

|-----------|-------|-----------|-----------------------------------------|------|

| Chapter 1 | Intro | duction   |                                         |      |

|           | 1.1   | Core C    | Dverview                                | 1-1  |

|           | 1.2   | Feature   | es Summary                              | 1-3  |

|           |       | 1.2.1     | General Architecture                    | 1-3  |

|           |       | 1.2.2     | Memory Organization                     | 1-4  |

|           |       | 1.2.3     | Physical Technology                     | 1-4  |

|           |       | 1.2.4     | Instruction Set Summary                 | 1-4  |

|           | 1.3   | CoreW     | /are Program                            | 1-6  |

| Chapter 2 | Fund  | ctional D | Description                             |      |

|           | 2.1   | Overvi    | ew                                      | 2-1  |

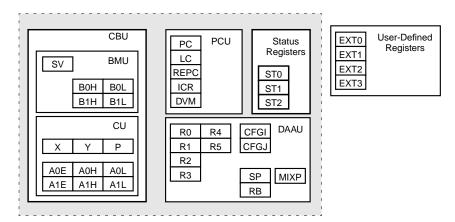

|           |       | 2.1.1     | CWDSP1650 Core Components               | 2-2  |

|           |       | 2.1.2     | CWDSP1650 External Modules              | 2-3  |

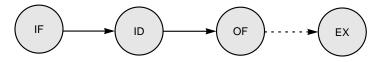

|           |       | 2.1.3     | Pipeline Architecture                   | 2-4  |

|           | 2.2   | Buses     |                                         | 2-5  |

|           |       | 2.2.1     | Data Buses                              | 2-5  |

|           |       | 2.2.2     | Address Buses                           | 2-5  |

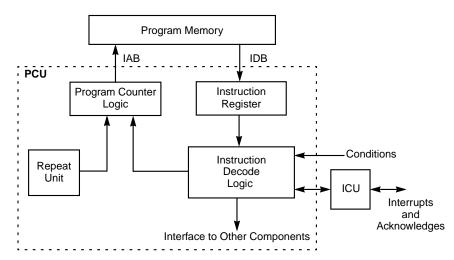

|           | 2.3   | Progra    | m Control Unit (PCU)                    | 2-6  |

|           |       | 2.3.1     | Interrupt Handling in the PCU           | 2-8  |

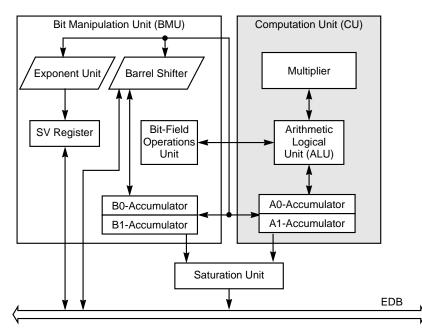

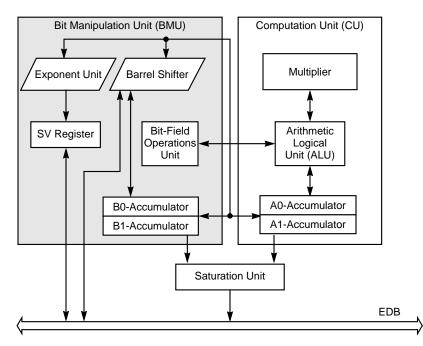

|           | 2.4   | Compu     | utation and Bit-Manipulation Unit (CBU) | 2-8  |

|           |       | 2.4.1     | Computation Unit                        | 2-8  |

|           |       | 2.4.2     | Bit-Manipulation Unit (BMU)             | 2-12 |

|           |       | 2.4.3     | Saturation Unit                         | 2-15 |

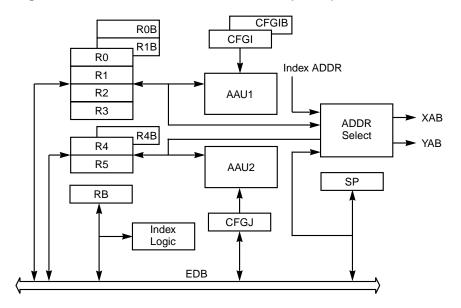

|           | 2.5   | Data A    | ddress Arithmetic Unit (DAAU)           | 2-17 |

|           |       | 2.5.1     | DAAU Registers                          | 2-18 |

|           |       | 2.5.2     | Addressing Modes                        | 2-19 |

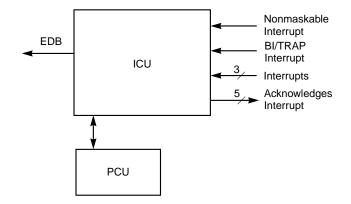

|           | 2.6   | Interru   | pt Control Unit (ICU)                   | 2-23 |

| Chapter 3 | Data Formats, Memory and Addressing |          |                                                     |            |  |

|-----------|-------------------------------------|----------|-----------------------------------------------------|------------|--|

|           | 3.1                                 | Data F   | ormats                                              | 3-1        |  |

|           | 3.2                                 | Progra   | m Memory                                            | 3-4        |  |

|           |                                     | 3.2.1    | Program Memory Addressing Modes                     | 3-5<br>3-5 |  |

|           | 3.3                                 | Data N   | lemory                                              |            |  |

|           |                                     | 3.3.1    | Data Memory Addressing Modes                        |            |  |

| Chapter 4 | Regi                                | isters   |                                                     |            |  |

|           | 4.1                                 | CBU R    | egisters                                            | 4-2        |  |

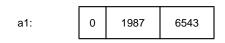

|           |                                     | 4.1.1    | Ax and Bx Accumulators                              | 4-2        |  |

|           |                                     | 4.1.2    | X, Y, and P Registers                               | 4-6        |  |

|           |                                     | 4.1.3    | Interrupt Context Switching Registers               | 4-7        |  |

|           |                                     | 4.1.4    | Shift Value Register                                | 4-9        |  |

|           | 4.2                                 | DAAU     | Registers                                           | 4-9        |  |

|           |                                     | 4.2.1    | Address Registers (R0-R5)                           | 4-10       |  |

|           |                                     | 4.2.2    | Configuration Registers                             | 4-11       |  |

|           |                                     | 4.2.3    | Base Register (RB)                                  | 4-11       |  |

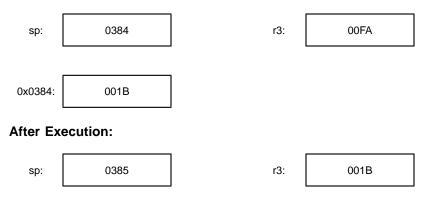

|           |                                     | 4.2.4    | Stack Pointer Register (SP)                         | 4-12       |  |

|           |                                     | 4.2.5    | Alternative Bank Registers                          | 4-12       |  |

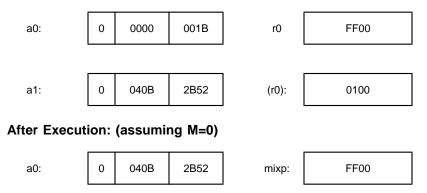

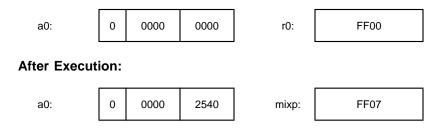

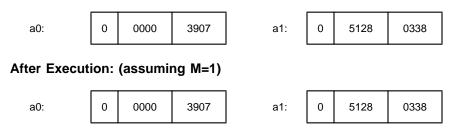

|           |                                     | 4.2.6    | Minimum/Maximum Pointer Latching Register<br>(MIXP) | 4-13       |  |

|           | 4.3                                 |          | legisters                                           | 4-13       |  |

|           | 1.0                                 | 4.3.1    | Data Value Match Register                           | 4-14       |  |

|           |                                     | 4.3.2    | -                                                   | 4-14       |  |

|           |                                     | 4.3.3    | Program and Loop Counters                           | 4-15       |  |

|           | 4.4                                 |          | Registers                                           | 4-16       |  |

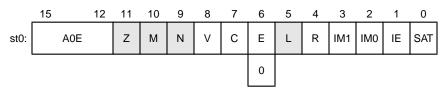

|           |                                     | 4.4.1    | Status Register 0 (ST0)                             | 4-16       |  |

|           |                                     | 4.4.2    |                                                     | 4-18       |  |

|           |                                     | 4.4.3    | Status Register 2 (ST2)                             | 4-19       |  |

|           | 4.5                                 |          | Defined Registers                                   | 4-21       |  |

| Chapter 5 | Sign                                | als      |                                                     |            |  |

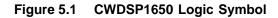

|           | 5.1                                 | Logic \$ | Symbol                                              | 5-1        |  |

|           | 5.2                                 | Bus In   | terface                                             | 5-3        |  |

|           | 5.3                                 | Progra   | m Control Interface                                 | 5-3        |  |

|           | 5.4                                 | Off-Co   | re Data Memory Interface                            | 5-4        |  |

|           | 5.5   | User-D   | efined Register Interface                 | 5-6  |

|-----------|-------|----------|-------------------------------------------|------|

|           | 5.6   | Emulat   | ion and Trace Buffer Interface            | 5-7  |

|           | 5.7   | Proces   | sor Control Interface                     | 5-9  |

|           | 5.8   | ScanIC   | E Control Interface                       | 5-10 |

|           | 5.9   | Clock (  | Control Interface                         | 5-11 |

| Chapter 6 | Ope   | ration   |                                           |      |

|           | 6.1   | Reset    |                                           | 6-1  |

|           | 6.2   | Boot P   | rocedure                                  | 6-2  |

|           | 6.3   | Interrup | ots                                       | 6-3  |

|           |       | 6.3.1    | Maskable Interrupts                       | 6-4  |

|           |       | 6.3.2    | Nonmaskable Interrupt (NMI)               | 6-6  |

|           |       | 6.3.3    | TRAP/BI Interrupts                        | 6-6  |

|           |       | 6.3.4    | Interrupt Protocol                        | 6-7  |

|           |       | 6.3.5    | Interrupt Priority                        | 6-9  |

|           |       | 6.3.6    | Context Switching                         | 6-9  |

|           |       | 6.3.7    | Interrupt Nesting                         | 6-10 |

|           |       | 6.3.8    | Interruptible State                       | 6-11 |

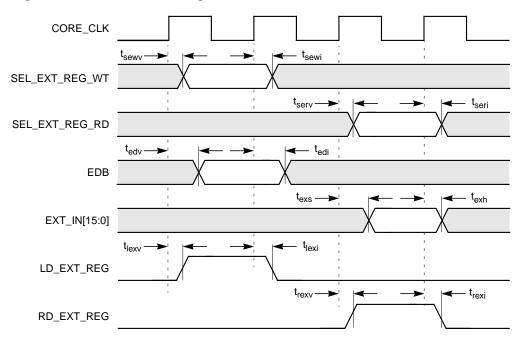

|           | 6.4   | Memor    | y Interface                               | 6-12 |

|           |       | 6.4.1    | Memory Interface with Slow Memory Devices | 6-14 |

|           | 6.5   | User-D   | efined Register Interface                 | 6-15 |

|           | 6.6   | Progra   | m Protection Mechanism                    | 6-16 |

|           | 6.7   | Clock (  | Control Unit (CCU)                        | 6-17 |

|           |       | 6.7.1    | CCU Operation                             | 6-18 |

|           |       | 6.7.2    | CCU Register                              | 6-19 |

| Chapter 7 | Instr | uction S | et                                        |      |

| -         | 7.1   | Notatio  | ns                                        | 7-1  |

|           |       | 7.1.1    | Register Notations                        | 7-1  |

|           |       | 7.1.2    | Number Representation                     | 7-3  |

|           |       | 7.1.3    | Data and Program Operands                 | 7-3  |

|           |       | 7.1.4    | Option Fields                             | 7-5  |

|           |       | 7.1.5    | Condition Field (cond) Notations          | 7-5  |

|           |       | 7.1.6    | Flag Notations                            | 7-6  |

|           |       | 7.1.7    | Miscellaneous Notations                   | 7-6  |

|           | 7.2   | Conver   | ntions and General Information            | 7-7  |

|           | 7.3   | Instruc  | tion Functional Groups                    | 7-10 |

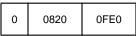

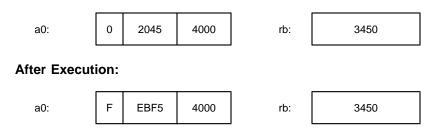

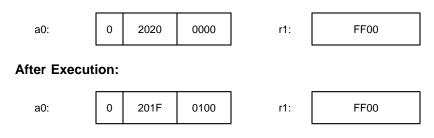

|           |      | 7.3.1   | Shift Operations                        | 7-14  |

|-----------|------|---------|-----------------------------------------|-------|

|           |      | 7.3.2   | Move and Shift Operations               | 7-15  |

|           |      | 7.3.3   | Rounding Operations                     | 7-16  |

|           |      | 7.3.4   | Division Step Operations                | 7-16  |

|           |      | 7.3.5   | Logical Operations                      | 7-16  |

|           |      | 7.3.6   | MAX and MIN Instructions                | 7-16  |

|           |      | 7.3.7   | Multiplication Instructions             | 7-17  |

|           | 7.4  | Instruc | tion Set List                           | 7-17  |

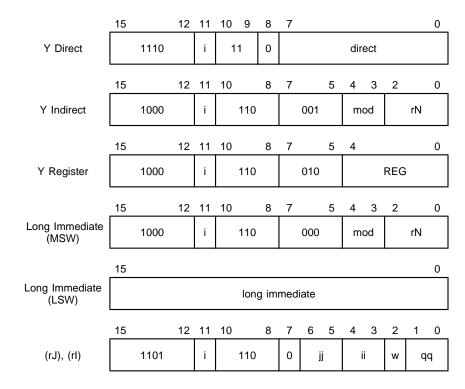

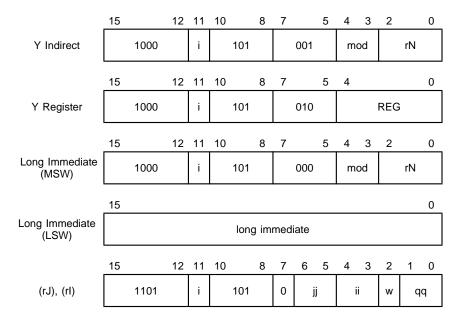

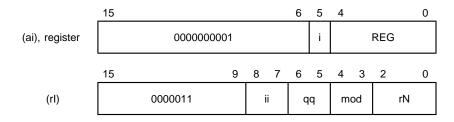

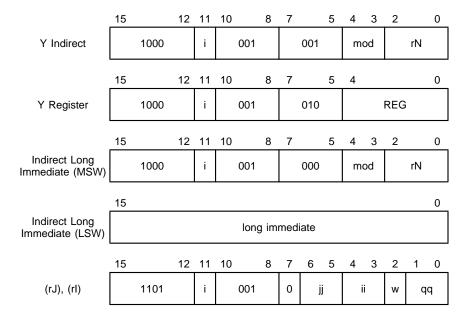

|           | 7.5  | Instruc | tion Opcode Bit Coding                  | 7-203 |

| Chapter 8 | On-( | Chip Em | ulation Module (OCEM)                   |       |

|           | 8.1  | OCEM    | Overview                                | 8-1   |

|           |      | 8.1.1   | Breakpoint Generation                   | 8-1   |

|           |      | 8.1.2   | Program Flow Tracing                    | 8-2   |

|           |      | 8.1.3   | ScanICE Debug Support                   | 8-2   |

|           |      | 8.1.4   | Suspended Mode Operation                | 8-3   |

|           | 8.2  | OCEM    | Programming Model                       | 8-3   |

|           |      | 8.2.1   | Status 0 Register                       | 8-4   |

|           |      | 8.2.2   | Status 1 Register                       | 8-6   |

|           |      | 8.2.3   | Mode Register                           | 8-7   |

|           |      | 8.2.4   | Data Address Breakpoint Register        | 8-9   |

|           |      | 8.2.5   | Data Address Mask Register              | 8-9   |

|           |      | 8.2.6   | Program Address Breakpoint Counters     | 8-10  |

|           |      | 8.2.7   | Program Address Breakpoint Registers    | 8-10  |

|           |      | 8.2.8   | Program Flow Trace Register and Program |       |

|           |      |         | Flow Trace Buffer                       | 8-10  |

|           | 8.3  | OCEM    | Signals                                 | 8-14  |

|           |      | 8.3.1   | Service Interface                       | 8-16  |

|           |      | 8.3.2   | Boot Logic Interface                    | 8-17  |

|           |      | 8.3.3   | Core Memory Bus Interface               | 8-18  |

|           |      | 8.3.4   | User-Defined Register Interface         | 8-19  |

|           |      | 8.3.5   | Illegal Access Interface                | 8-19  |

|           |      | 8.3.6   | Core Control Interface                  | 8-20  |

|           |      | 8.3.7   | Breakpoint Interface                    | 8-21  |

|           |      | 8.3.8   | ScanICE Interface                       | 8-22  |

|           |      | 8.3.9   | Clocking and Miscellaneous OCEM Signals | 8-23  |

|           | 8.4  | OCEM    | Breakpoints                             | 8-24  |

|           |      | 8.4.1   | Program Address Breakpoint              | 8-24  |

| 8.4.4       Combined Data Address and Data Value<br>Breakpoints       8         8.4.5       External Register Breakpoint       8         8.4.6       Abort Breakpoint       8         8.4.7       Illegal Access Breakpoint       8         8.4.8       Branch and Block Repeat Breakpoint       8         8.4.9       Interrupt Breakpoint       8         8.4.10       Single-Step Operation       8         8.4.11       Program Flow Trace Buffer Full Breakpoint       8         8.4.11       Program Flow Trace Buffer Full Breakpoint       8         9.1       ScanICE       9.1       ScanICE Requirements         9.3       ScanICE Interface       9.3.1       Scan Control Register         9.3.2       ScanICE Control       9.3.3       External Scan Logic Control         9.3.3       External Scan Logic Control       9         9.4       CWDSP1650 ScanICE Support       9         9.4.1       OCEM ScanICE Support       9         9.4       CCU ScanICE Support       9         9.5       Memory Access during ScanICE       9         9.6       ScanICE Reset       9         9.6       ScanICE Reset       9         9.6       ScanICE Reset       9 |            |                | 8.4.2   | Data Address Breakpoint                   | 8-26 |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|----------------|---------|-------------------------------------------|------|--|

| Breakpoints       8         8.4.5       External Register Breakpoint       8         8.4.6       Abort Breakpoint       8         8.4.7       Illegal Access Breakpoint       8         8.4.8       Branch and Block Repeat Breakpoint       8         8.4.9       Interrupt Breakpoint       8         8.4.9       Interrupt Breakpoint       8         8.4.10       Single-Step Operation       8         8.4.11       Program Flow Trace Buffer Full Breakpoint       8         Chapter 9         ScanICE         9.1       ScanICE Requirements         9.3       ScanICE Interface       9.3.1         9.3       ScanICE Control       9         9.3.4       Clock Gating       9         9.4       CWDSP1650 ScanICE Support       9         9.4.1       OCEM ScanICE Support       9         9.4.2       CCU ScanICE Support       9         9.4.3       OCEM ScanICE       9         9.4       CWDSP1650 ScanICE Support       9         9.4.1       OCEM ScanICE Support       9         9.5       Memory Access during ScanICE       9         9.6       ScanICE Reset       9     <                                                                              |            |                | 8.4.3   | Data Value Breakpoint                     | 8-26 |  |

| 8.4.5       External Register Breakpoint       8         8.4.6       Abort Breakpoint       8         8.4.7       Illegal Access Breakpoint       8         8.4.8       Branch and Block Repeat Breakpoints       8         8.4.9       Interrupt Breakpoint       8         8.4.10       Single-Step Operation       8         8.4.11       Program Flow Trace Buffer Full Breakpoint       8         Chapter 9         ScanICE         9.1       ScanICE Requirements         9.3       ScanICE Interface       9.3.1         9.3       ScanICE Control       9         9.3.1       Scan Control Register       9         9.3.2       ScanICE Control       9         9.3.3       External Scan Logic Control       9         9.4       CWDSP1650 ScanICE Support       9         9.4.1       OCEM ScanICE Support       9         9.4.2       CCU ScanICE Support       9         9.5       Memory Access during ScanICE       9         9.6       ScanICE Reset       9         Chapter 10         Specifications         10.1       Physical Specifications       1                                                                                                    |            |                | 8.4.4   | Combined Data Address and Data Value      |      |  |

| 8.4.6       Abort Breakpoint       8         8.4.7       Illegal Access Breakpoint       8         8.4.8       Branch and Block Repeat Breakpoints       8         8.4.9       Interrupt Breakpoint       8         8.4.10       Single-Step Operation       8         8.4.11       Program Flow Trace Buffer Full Breakpoint       8         Chapter 9         ScanICE         9.1       ScanICE Requirements         9.2       ScanICE Interface       9.3.1         9.3.1       Scan Control Register       9.3.2         9.3.2       ScanICE Control       9.3.3         9.3.4       Clock Gating       9         9.4       CWDSP1650 ScanICE Support       9         9.4.1       OCEM ScanICE Support       9         9.4.2       CCU ScanICE Support       9         9.5       Memory Access during ScanICE       9         9.6       ScanICE Reset       9         Chapter 10         Specifications         10.1       Physical Specifications       1         10.2       AC Timing Diagrams       1         10.2.1       OCEM Registers       1         10.2.2                                                                                                     |            |                |         | Breakpoints                               | 8-27 |  |

| 8.4.7       Illegal Access Breakpoint       8         8.4.8       Branch and Block Repeat Breakpoints       8         8.4.9       Interrupt Breakpoint       8         8.4.10       Single-Step Operation       8         8.4.11       Program Flow Trace Buffer Full Breakpoint       8         Chapter 9         ScanICE         9.1       ScanICE Requirements         9.2       ScanICE Interface       9.3.1         9.3.1       Scan Control Register       9.3.2         9.3.3       External Scan Logic Control       9         9.3.4       Clock Gating       9         9.4       CWDSP1650 ScanICE Support       9         9.4.1       OCEM ScanICE Support       9         9.5       Memory Access during ScanICE       9         9.6       ScanICE Reset       9         Chapter 10         Specifications         10.1       Physical Specifications       1         10.2       AC Timing Diagrams       1         10.2.2       Data and Program Memory       1                                                                                                                                                                                                |            |                | 8.4.5   | External Register Breakpoint              | 8-27 |  |

| 8.4.8       Branch and Block Repeat Breakpoints       8         8.4.9       Interrupt Breakpoint       8         8.4.10       Single-Step Operation       8         8.4.11       Program Flow Trace Buffer Full Breakpoint       8         Chapter 9         ScanICE         9.1       ScanICE Requirements         9.2       ScanICE Interface       9.3.1         9.3.1       Scan Control Register       9.3.2         9.3.3       External Scan Logic Control       9         9.4       Clock Gating       9         9.4.1       OCEM ScanICE Support       9         9.4.1       OCEM ScanICE Support       9         9.4.1       OCEM ScanICE Support       9         9.5       Memory Access during ScanICE       9         9.6       ScanICE Reset       9         Chapter 10         Specifications         10.1       Physical Specifications       1         10.2       AC Timing Diagrams       1         10.2.2       Data and Program Memory       1                                                                                                                                                                                                          |            |                | 8.4.6   | Abort Breakpoint                          | 8-27 |  |

| 8.4.9       Interrupt Breakpoint       8         8.4.10       Single-Step Operation       8         8.4.11       Program Flow Trace Buffer Full Breakpoint       8         Chapter 9         ScanICE         9.1       ScanICE Requirements         9.2       ScanICE Interface       9.3.1         9.3       ScanICE Interface       9.3.2         9.3.1       Scan Control Register       9.3.2         9.3.2       ScanICE Control       9         9.3.4       Clock Gating       9         9.4       CWDSP1650 ScanICE Support       9         9.4.1       OCEM ScanICE Support       9         9.5       Memory Access during ScanICE       9         9.6       ScanICE Reset       9         Chapter 10         Specifications         10.1       Physical Specifications       1         10.2       AC Timing Diagrams       1         10.2.1       OCEM Registers       1         10.2.2       Data and Program Memory       1                                                                                                                                                                                                                                      |            |                | 8.4.7   | Illegal Access Breakpoint                 | 8-28 |  |

| 8.4.10       Single-Step Operation       8         8.4.11       Program Flow Trace Buffer Full Breakpoint       8         Chapter 9         ScanICE       9.1       ScanICE Power Saving Registers         9.2       ScanICE Requirements       9.3       ScanICE Interface         9.3.1       Scan Control Register       9.3.2       ScanICE Control         9.3.3       External Scan Logic Control       9         9.4       CWDSP1650 ScanICE Support       9         9.4.1       OCEM ScanICE Support       9         9.4.2       CCU ScanICE Support       9         9.5       Memory Access during ScanICE       9         9.6       ScanICE Reset       9         Chapter 10         Specifications         10.2       AC Timing Diagrams       1         10.2.1       OCEM Registers       1         10.2.2       Data and Program Memory       1                                                                                                                                                                                                                                                                                                                |            |                | 8.4.8   | Branch and Block Repeat Breakpoints       | 8-28 |  |

| 8.4.11       Program Flow Trace Buffer Full Breakpoint       8         Chapter 9       ScanICE       9.1       ScanICE Power Saving Registers         9.2       ScanICE Requirements       9.3       ScanICE Interface         9.3.1       Scan Control Register       9.3.2       ScanICE Control         9.3.3       External Scan Logic Control       9         9.4.4       Clock Gating       9         9.4.1       OCEM ScanICE Support       9         9.4.1       OCEM ScanICE Support       9         9.4.2       CCU ScanICE Support       9         9.5       Memory Access during ScanICE       9         9.6       ScanICE Reset       9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |            |                | 8.4.9   | Interrupt Breakpoint                      | 8-29 |  |

| Chapter 9       ScanICE         9.1       ScanICE Power Saving Registers         9.2       ScanICE Requirements         9.3       ScanICE Interface         9.3.1       Scan Control Register         9.3.2       ScanICE Control         9.3.3       External Scan Logic Control         9.3.4       Clock Gating         9.4       CWDSP1650 ScanICE Support         9.4.1       OCEM ScanICE Support         9.4.2       CCU ScanICE Support         9.5       Memory Access during ScanICE         9.6       ScanICE Reset             Chapter 10       Specifications         10.1       Physical Specifications         10.2       AC Timing Diagrams         10.2.1       OCEM Registers         10.2.2       Data and Program Memory                                                                                                                                                                                                                                                                                                                                                                                                                                |            |                | 8.4.10  | Single-Step Operation                     | 8-29 |  |

| 9.1       ScanICE Power Saving Registers         9.2       ScanICE Interface         9.3       ScanICE Interface         9.3.1       Scan Control Register         9.3.2       ScanICE Control         9.3.3       External Scan Logic Control         9.3.4       Clock Gating         9.4       CWDSP1650 ScanICE Support         9.4.1       OCEM ScanICE Support         9.4.2       CCU ScanICE Support         9.5       Memory Access during ScanICE         9.6       ScanICE Reset             Chapter 10       Specifications         10.1       Physical Specifications       1         10.2       AC Timing Diagrams       1         10.2.1       OCEM Registers       1         10.2.2       Data and Program Memory       1                                                                                                                                                                                                                                                                                                                                                                                                                                   |            |                | 8.4.11  | Program Flow Trace Buffer Full Breakpoint | 8-29 |  |

| 9.2       ScanICE Requirements         9.3       ScanICE Interface         9.3.1       Scan Control Register         9.3.2       ScanICE Control         9.3.3       External Scan Logic Control         9.3.4       Clock Gating         9.4       CWDSP1650 ScanICE Support         9.4.1       OCEM ScanICE Support         9.4.2       CCU ScanICE Support         9.5       Memory Access during ScanICE         9.6       ScanICE Reset             Chapter 10       Specifications         10.1       Physical Specifications         10.2       AC Timing Diagrams         10.2.1       OCEM Registers         10.2.2       Data and Program Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Chapter 9  | Scan           | ICE     |                                           |      |  |

| 9.3       ScanICE Interface         9.3.1       Scan Control Register         9.3.2       ScanICE Control         9.3.3       External Scan Logic Control         9.3.4       Clock Gating         9.4       CWDSP1650 ScanICE Support         9.4.1       OCEM ScanICE Support         9.4.2       CCU ScanICE Support         9.5       Memory Access during ScanICE         9.6       ScanICE Reset             Chapter 10             Specifications         10.1       Physical Specifications         10.2       AC Timing Diagrams         10.2.1       OCEM Registers         10.2.2       Data and Program Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |            | 9.1            | ScanIC  | E Power Saving Registers                  | 9-2  |  |

| 9.3.1       Scan Control Register         9.3.2       ScanICE Control         9.3.3       External Scan Logic Control         9.3.4       Clock Gating         9.4       CWDSP1650 ScanICE Support         9.4.1       OCEM ScanICE Support         9.4.2       CCU ScanICE Support         9.5       Memory Access during ScanICE         9.6       ScanICE Reset         Chapter 10         Specifications         10.1       Physical Specifications         10.2       AC Timing Diagrams         10.2.1       OCEM Registers         10.2.2       Data and Program Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |            | 9.2            | ScanIC  | E Requirements                            | 9-4  |  |

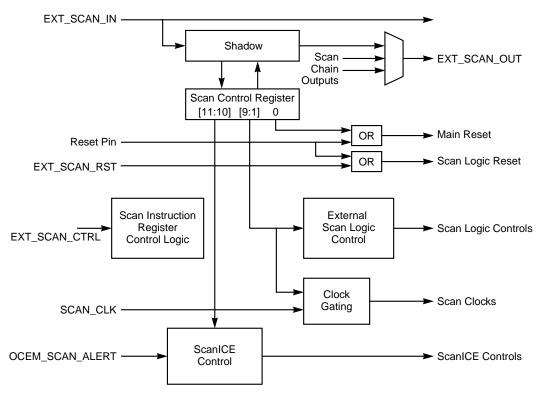

| 9.3.2       ScanICE Control         9.3.3       External Scan Logic Control         9.3.4       Clock Gating         9.4       CWDSP1650 ScanICE Support         9.4.1       OCEM ScanICE Support         9.4.2       CCU ScanICE Support         9.5       Memory Access during ScanICE         9.6       ScanICE Reset         9.6       ScanICE Reset         9.7       Physical Specifications         10.1       Physical Specifications         10.2       AC Timing Diagrams         10.2.1       OCEM Registers         10.2.2       Data and Program Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |            | 9.3            | ScanIC  | E Interface                               | 9-6  |  |

| 9.3.3       External Scan Logic Control       9         9.3.4       Clock Gating       9         9.4       CWDSP1650 ScanICE Support       9         9.4.1       OCEM ScanICE Support       9         9.4.2       CCU ScanICE Support       9         9.5       Memory Access during ScanICE       9         9.6       ScanICE Reset       9         Chapter 10         Specifications         10.1       Physical Specifications       1         10.2       AC Timing Diagrams       1         10.2.1       OCEM Registers       1         10.2.2       Data and Program Memory       1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |            |                | 9.3.1   | Scan Control Register                     | 9-7  |  |

| 9.3.4 Clock Gating<br>9.4 CWDSP1650 ScanICE Support<br>9.4.1 OCEM ScanICE Support<br>9.4.2 CCU ScanICE Support<br>9.5 Memory Access during ScanICE<br>9.6 ScanICE Reset<br>Chapter 10 Specifications<br>10.1 Physical Specifications<br>10.2 AC Timing Diagrams<br>10.2.1 OCEM Registers<br>10.2.2 Data and Program Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |            |                | 9.3.2   | ScanICE Control                           | 9-9  |  |

| 9.4       CWDSP1650 ScanICE Support       9         9.4.1       OCEM ScanICE Support       9         9.4.2       CCU ScanICE Support       9         9.5       Memory Access during ScanICE       9         9.6       ScanICE Reset       9         Chapter 10         Specifications         10.1       Physical Specifications       1         10.2       AC Timing Diagrams       1         10.2.1       OCEM Registers       1         10.2.2       Data and Program Memory       1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |            |                | 9.3.3   | External Scan Logic Control               | 9-11 |  |

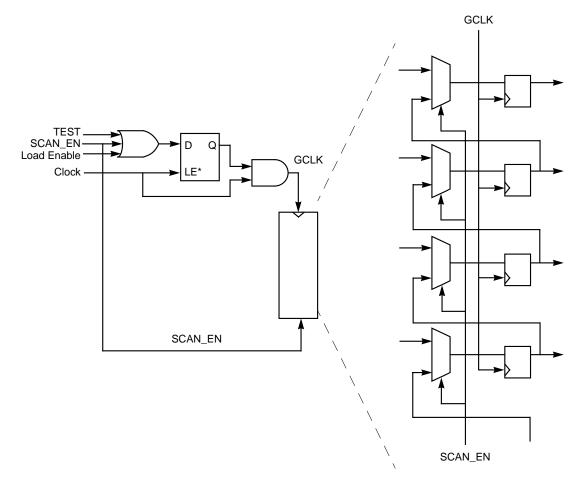

| 9.4.1       OCEM ScanICE Support       9         9.4.2       CCU ScanICE Support       9         9.5       Memory Access during ScanICE       9         9.6       ScanICE Reset       9         Chapter 10         Specifications         10.1       Physical Specifications       1         10.2       AC Timing Diagrams       1         10.2.1       OCEM Registers       1         10.2.2       Data and Program Memory       1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |            |                | 9.3.4   | Clock Gating                              | 9-12 |  |

| 9.4.2 CCU ScanICE Support<br>9.5 Memory Access during ScanICE<br>9.6 ScanICE Reset<br>Chapter 10 Specifications<br>10.1 Physical Specifications<br>10.2 AC Timing Diagrams<br>10.2.1 OCEM Registers<br>10.2.2 Data and Program Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |            | 9.4            | CWDSF   | P1650 ScanICE Support                     | 9-12 |  |

| 9.5       Memory Access during ScanICE       9         9.6       ScanICE Reset       9         Chapter 10       Specifications         10.1       Physical Specifications       1         10.2       AC Timing Diagrams       1         10.2.1       OCEM Registers       1         10.2.2       Data and Program Memory       1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |            |                | 9.4.1   | OCEM ScanICE Support                      | 9-12 |  |

| 9.6       ScanICE Reset       9         Chapter 10       Specifications       1         10.1       Physical Specifications       1         10.2       AC Timing Diagrams       1         10.2.1       OCEM Registers       1         10.2.2       Data and Program Memory       1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |            |                | 9.4.2   | CCU ScanICE Support                       | 9-12 |  |

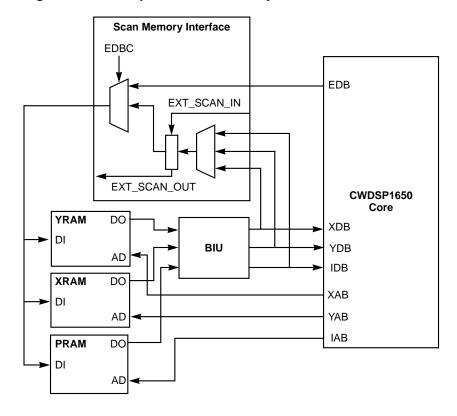

| Chapter 10       Specifications         10.1       Physical Specifications       1         10.2       AC Timing Diagrams       1         10.2.1       OCEM Registers       1         10.2.2       Data and Program Memory       1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |            | 9.5            | Memory  | Access during ScanICE                     | 9-13 |  |

| 10.1Physical Specifications110.2AC Timing Diagrams110.2.1OCEM Registers110.2.2Data and Program Memory1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |            | 9.6            | ScanIC  | E Reset                                   | 9-15 |  |

| 10.2AC Timing Diagrams110.2.1OCEM Registers110.2.2Data and Program Memory1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Chapter 10 | Specifications |         |                                           |      |  |

| 10.2.1OCEM Registers110.2.2Data and Program Memory1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |            | 10.1           | Physica | I Specifications                          | 10-1 |  |

| 10.2.2 Data and Program Memory 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |            | 10.2           | AC Tim  | ing Diagrams                              | 10-1 |  |

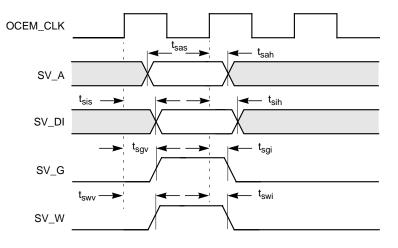

| <b>o ,</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |            |                | 10.2.1  | OCEM Registers                            | 10-2 |  |

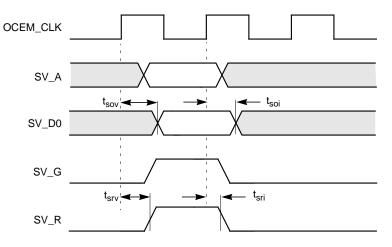

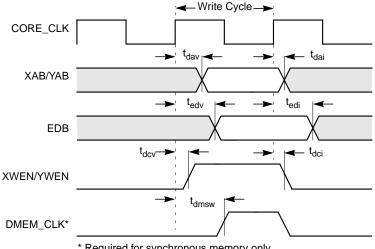

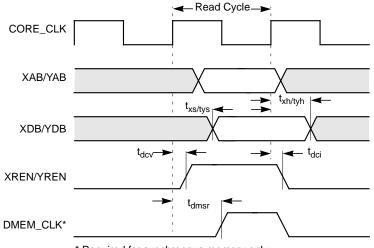

| 10.2.3     User-Defined Registers     1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |            |                | 10.2.2  | Data and Program Memory                   | 10-4 |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |            |                | 10.2.3  | User-Defined Registers                    | 10-9 |  |

| Appendix A CWDSP1650 Register Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Appendix A | CWD            | SP1650  | Register Summary                          |      |  |

### **Customer Feedback**

### Figures

| 1.1  | CWDSP1650 Block Diagram                     | 1-2  |

|------|---------------------------------------------|------|

| 2.1  | CWDSP1650 Block Diagram                     | 2-2  |

| 2.2  | CWDSP1650 Instruction Pipeline              | 2-4  |

| 2.3  | Program Control Unit Diagram                | 2-6  |

| 2.4  | CU Block Diagram                            | 2-9  |

| 2.5  | BMU Block Diagram                           | 2-13 |

| 2.6  | Data Address Arithmetic Unit (DAAU)         | 2-17 |

| 2.7  | Interrupt Control Unit                      | 2-23 |

| 3.1  | Signed and Unsigned Integer Formats         | 3-2  |

| 3.2  | Program Memory Map                          | 3-4  |

| 4.1  | CWDSP1650 Registers                         | 4-1  |

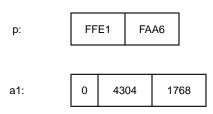

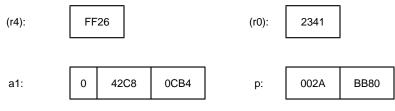

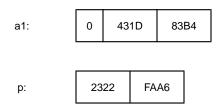

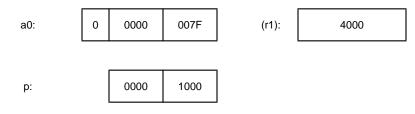

| 4.2  | P Register                                  | 4-7  |

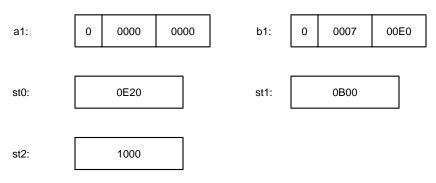

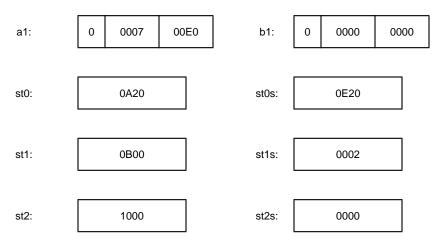

| 4.3  | ST0 and Shadow Registers                    | 4-8  |

| 4.4  | ST1 and Shadow Registers                    | 4-8  |

| 4.5  | ST2 and Shadow Registers                    | 4-9  |

| 4.6  | CFGI Configuration Register                 | 4-11 |

| 4.7  | CFGJ Configuration Register                 | 4-11 |

| 4.8  | Internal Configuration Register (ICR)       | 4-14 |

| 4.9  | Status Register 0 (ST0)                     | 4-16 |

| 4.10 | Status Register 1 (ST1)                     | 4-18 |

| 4.11 | Status Register 2 (ST2)                     | 4-19 |

| 5.1  | CWDSP1650 Logic Symbol                      | 5-2  |

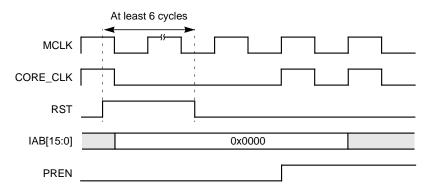

| 6.1  | Reset Operation                             | 6-2  |

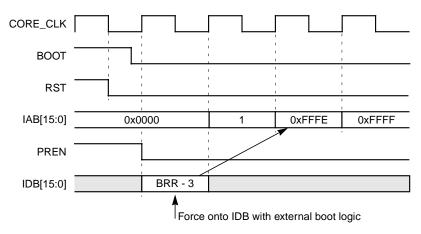

| 6.2  | Entering Boot Mode                          | 6-3  |

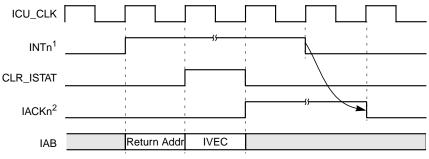

| 6.3  | Interrupt Protocol                          | 6-7  |

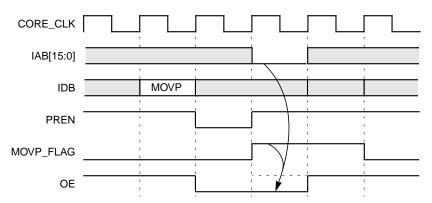

| 6.4  | Memory Protection Mechanism                 | 6-17 |

| 6.5  | CCU Register                                | 6-19 |

| 7.1  | Arithmetic Shift Right                      | 7-15 |

| 7.2  | Logical Shift Right                         | 7-15 |

| 7.3  | Arithmetic and Logical Shift Left           | 7-15 |

| 8.1  | Status 0 Register                           | 8-4  |

| 8.2  | Status 1 Register                           | 8-6  |

| 8.3  | Mode Register                               | 8-7  |

| 8.4  | Program Flow Trace with Corresponding Trace |      |

|      | Buffer Entries                              | 8-13 |

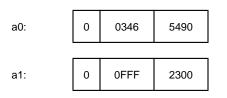

| 9.1  | Power Saving Register with Scan Inserted    | 9-2  |

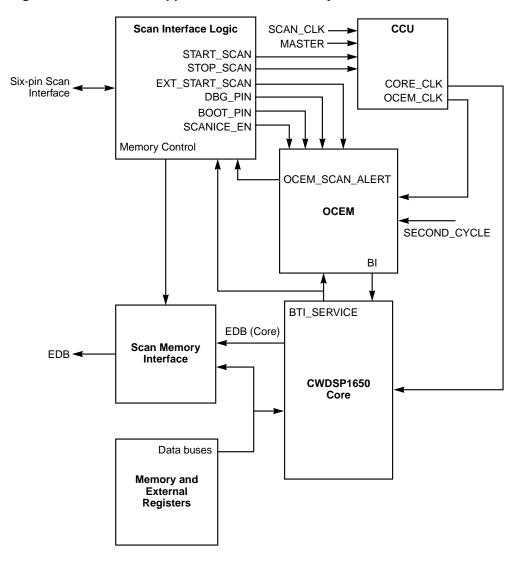

| ScanICE Support in a CWDSP1650 System      | 9-5                                                                                                                                                                                                                                                                                                                                                  |

|--------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

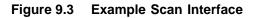

| Example Scan Interface                     | 9-7                                                                                                                                                                                                                                                                                                                                                  |

| Scan Control Register                      | 9-8                                                                                                                                                                                                                                                                                                                                                  |

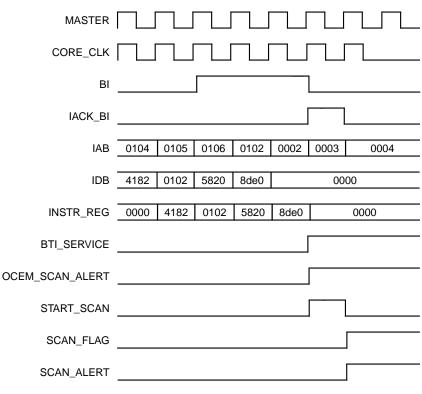

| Entry to Scan Using a Breakpoint Interrupt | 9-10                                                                                                                                                                                                                                                                                                                                                 |

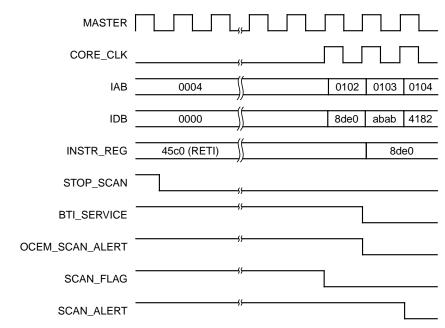

| Stop Scan Mode                             | 9-11                                                                                                                                                                                                                                                                                                                                                 |

| Example ScanICE Memory Access Scheme       | 9-14                                                                                                                                                                                                                                                                                                                                                 |

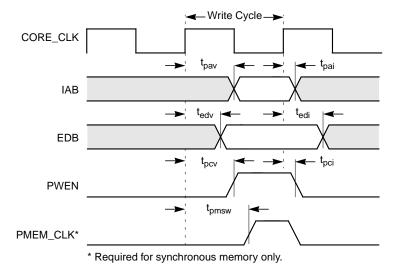

| Writing the OCEM                           | 10-2                                                                                                                                                                                                                                                                                                                                                 |

| Reading the OCEM                           | 10-3                                                                                                                                                                                                                                                                                                                                                 |

| Data Memory Write Access                   | 10-4                                                                                                                                                                                                                                                                                                                                                 |

| Data Memory Read Access                    | 10-5                                                                                                                                                                                                                                                                                                                                                 |

| Program Memory Write Access                | 10-5                                                                                                                                                                                                                                                                                                                                                 |

| Program Memory Read Access                 | 10-6                                                                                                                                                                                                                                                                                                                                                 |

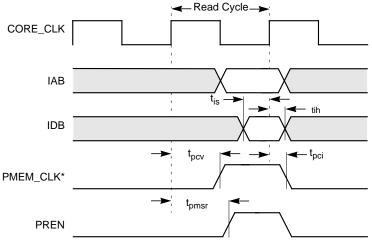

| Memory Access with Wait State              | 10-7                                                                                                                                                                                                                                                                                                                                                 |

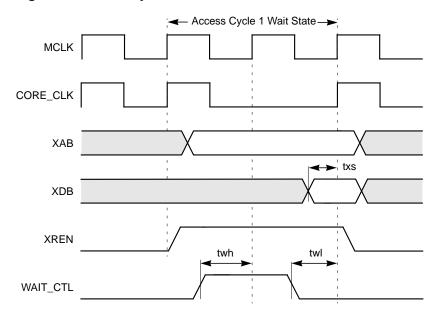

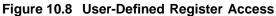

| User-Defined Register Access               | 10-9                                                                                                                                                                                                                                                                                                                                                 |

|                                            | Example Scan Interface<br>Scan Control Register<br>Entry to Scan Using a Breakpoint Interrupt<br>Stop Scan Mode<br>Example ScanICE Memory Access Scheme<br>Writing the OCEM<br>Reading the OCEM<br>Data Memory Write Access<br>Data Memory Read Access<br>Program Memory Write Access<br>Program Memory Read Access<br>Memory Access with Wait State |

### Tables

| 1.1  | CWDSP1650 Instruction Set Summary             | 1-5  |

|------|-----------------------------------------------|------|

| 2.1  | Multiplier Unit Instructions                  | 2-11 |

| 2.2  | Saturation Overflow                           | 2-16 |

| 2.3  | Indirect Addressing Mode Bits                 | 2-20 |

| 3.1  | Signed and Unsigned Integer Ranges            | 3-3  |

| 3.2  | Data Memory Address Mapping                   | 3-6  |

| 3.3  | Short Direct Addressing Page Values           | 3-7  |

| 4.1  | CBU Registers                                 | 4-2  |

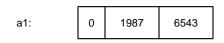

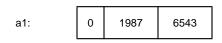

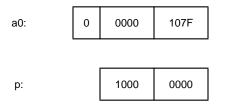

| 4.2  | Ax and Bx Accumulator Organization            | 4-3  |

| 4.3  | Ax Accumulator Loading Values                 | 4-4  |

| 4.4  | Bx Accumulator Loading Values                 | 4-5  |

| 4.5  | DAAU Registers                                | 4-10 |

| 4.6  | Rn Register Grouping                          | 4-10 |

| 4.7  | Validity of STEP and MODULO in Different      |      |

|      | Addressing Modes                              | 4-11 |

| 4.8  | Alternative Bank Registers                    | 4-13 |

| 4.9  | PCU Registers                                 | 4-13 |

| 4.10 | Status Registers                              | 4-16 |

| 6.1  | Maskable Interrupt Bits and Signals           | 6-5  |

| 6.2  | Interrupts and Priorities                     | 6-9  |

| 6.3  | Interrupt Latency after Specific Instructions | 6-12 |

| 6.4  | Data Memory Space Partitioning                | 6-13 |

| 6.5  | Memory Signals Interface                       | 6-14  |

|------|------------------------------------------------|-------|

| 6.6  | Example for Defining the Number of Wait Cycles | 6-15  |

| 6.7  | User-Defined Register Coding                   | 6-16  |

| 6.8  | CCU Output Clocks                              | 6-18  |

| 7.1  | Register Notations                             | 7-1   |

| 7.2  | Program Operand Notation                       | 7-3   |

| 7.3  | Data Operand Notation                          | 7-4   |

| 7.4  | Option Field Notations                         | 7-5   |

| 7.5  | Condition Field Notations                      | 7-5   |

| 7.6  | Miscellaneous Notations                        | 7-6   |

| 7.7  | CWDSP1650 Instruction Set Listing              | 7-10  |

| 7.8  | Opcode i                                       | 7-203 |

| 7.9  | Opcode i or j                                  | 7-203 |

| 7.10 | Opcode AB                                      | 7-203 |

| 7.11 | Opcode ABL                                     | 7-204 |

| 7.12 | Opcode rn                                      | 7-204 |

| 7.13 | Opcode rn*                                     | 7-204 |

| 7.14 | Opcode mod                                     | 7-205 |

| 7.15 | Opcode w                                       | 7-205 |

| 7.16 | Opcode REG/reg                                 | 7-205 |

| 7.17 | Opcode ii                                      | 7-206 |

| 7.18 | Opcode jj                                      | 7-206 |

| 7.19 | Opcode qq                                      | 7-207 |

| 7.20 | Opcode cond                                    | 7-207 |

| 7.21 | Opcode x                                       | 7-207 |

| 7.22 | Opcode bank in BANKE Instructions              | 7-208 |

| 7.23 | Opcode ext                                     | 7-208 |

| 7.24 | Opcode bbbb                                    | 7-208 |

| 8.1  | OCEM Programming Model                         | 8-3   |

| 8.2  | OCEM Signal List                               | 8-14  |

| 8.3  | Program Address Breakpoint Components          | 8-25  |

| 9.1  | ScanICE Operational Modes                      | 9-3   |

| 9.2  | Six-pin ScanICE Interface                      | 9-6   |

| 10.1 | CWDSP1650 Physical Layout Size                 | 10-1  |

| 10.2 | OCEM Access Timing Constraints                 | 10-3  |

| 10.3 | Memory Interface Timing Constraints            | 10-7  |

| 10.4 | User-Defined Register Interface Timing Values  | 10-10 |

| A.1  | CWDSP1650 Registers                            | A-1   |

### Preface

This book is the primary reference and technical manual for LSI Logic's CWDSP1650 DSP Core. It contains a complete functional description for the core and includes both physical and electrical specifications.

### Audience

This document assumes that the reader has some familiarity with digital signal processors. The people who benefit the most from this book are:

- Engineers and managers who are evaluating the CWDSP1650 for possible use in a design

- Engineers who are designing the CWDSP1650 into a chip

Engineers who are familiar with the CWDSP1640 can refer to the *Comparison of the CWDSP1640 and CWDSP1650 Cores Technical Note* for a full review of any design changes.

#### Organization

This document has the following chapters and appendixes:

- Chapter 1, Introduction, discusses the CWDSP1650 in general, provides the core's key features, and discusses the CoreWare<sup>®</sup> program.

- Chapter 2, Functional Description, describes the purpose of each component block in the CWDSP1650.

- Chapter 3, Data Formats, Memory and Addressing, describes the six supported data formats, the program and data memory spaces, and the addressing modes.

- Chapter 4, Registers, defines the CWDSP1650 registers and describes the register bit fields.

- Chapter 5, Signals, describes the input, output, and bidirectional signals of the CWDSP1650 core.

- Chapter 6, Operation, describes the operation of the CWDSP1650 input/output interface.

- Chapter 7, Instruction Set, provides a detailed description of the CWDSP1650 instruction set.

- Chapter 8, On-Chip Emulation Module (OCEM), describes the optional module that provides on-chip emulation for a CWDSP1650-based chip.

- Chapter 9, ScanICE, describes the CWDSP1650 ScanICE components and describes an example ScanICE system design.

- Chapter 10, Specifications, contains the physical characteristics and AC timing for the CWDSP1650 core.

- Appendix A, CWDSP1650 Register Summary, lists all of the CWDSP1650 registers and where a detailed description for each can be found.

- Customer Feedback, includes a form that you may use to fax us your comments about this document.

### **Related Publications**

*CWDSP1640 OakDSPCore*<sup>®</sup> *Assembler and Linker User's Guide*, Order No. C14029

*CWDSP1640 OakDSPCore*<sup>®</sup> *C Cross Compiler User's Guide*, Order No. C14026.A

*CWDSP1640 OakDSPCore*<sup>®</sup> *Debugger User's Guide*, Order No. C14027.A

CWDSP1650 Reference Device User's Guide, available from LSI Logic.

CWDSP1650 Evaluation Kit User's Guide, Order No. C14046

*Comparison of the CWDSP1640 and CWDSP1650 Cores Technical Note*, Order No. C15030

### **Conventions Used in This Manual**

The first time a word or phrase is defined in this manual, it is *italicized*.

The word *assert* means to drive a signal true or active. The word *deassert* means to drive a signal false or inactive.

Hexadecimal numbers are indicated by the prefix "0x", for example, 0x32CF. Binary numbers are indicated by the prefix "0b", for example, 0b0011 0010 1100 1111.

### Chapter 1 Introduction

This chapter overviews LSI Logic's CWDSP1650 DSP core and contains the following sections:

- Section 1.1, "Core Overview"

- Section 1.2, "Features Summary"

- Section 1.3, "CoreWare Program"

### 1.1 Core Overview

The CWDSP1650 is a 16-bit, fixed-point digital signal processor (DSP) core designed for middle-end to high-end telecommunications and consumer applications. This core provides a low-cost, high-performance solution for applications where low-power and portability are a necessity. This core is a component of the LSI Logic CoreWare Library, which contains cores for control, high-speed communication, and mixed-signal functions to complement quick time-to-market, customizable solutions. The CWDSP1650 is designed by LSI Logic to be fully compatible with the DSP Group OakDSPCore<sup>®</sup> Instruction Set architecture. The Oak family of cores are modified Harvard architectures, based on DSP Group's PineDSPCore<sup>®</sup> architecture.

The CWDSP1650 architecture contains dedicated buses, program memories, and data memories. The core is composed of three major components:

- Data Address Arithmetic Unit (DAAU)

- Program Control Unit (PCU)

- Computation and Bit Manipulation Unit (CBU)

The CBU includes a Multiplier, an Arithmetic Logical Unit (ALU), and the Bit Manipulation Unit (BMU). A multiply-accumulate unit performs single-cycle operations.

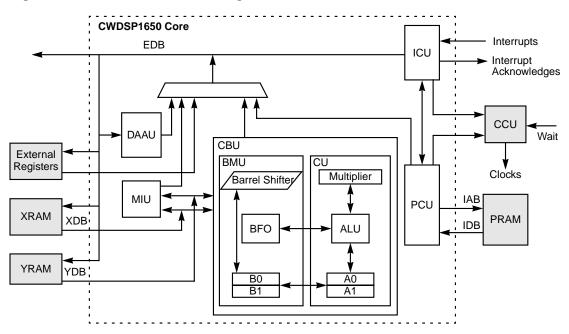

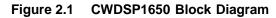

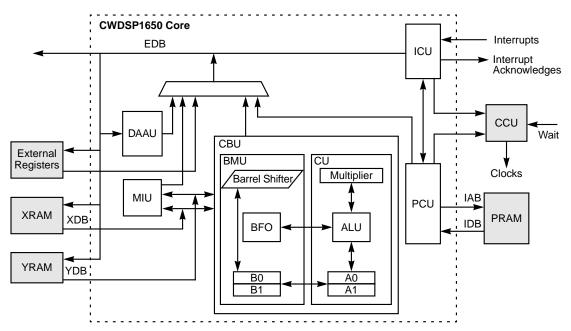

Figure 1.1 shows a block diagram of the CWDSP1650 core, with modules external to the core shown as shaded regions. Any of the external modules are available as hardmacros from LSI Logic and do not need to be generated by the designer.

### Figure 1.1 CWDSP1650 Block Diagram

The CWDSP1650 instruction set allows for straight-forward generation of efficient and compact code for implementation of the DSP functions within a system. Designers may also integrate multiple OakDSPCores onto a single piece of silicon along with other ASIC functions, processors such as the ARM7TDMI core, and application specific logic to build a system-on-a-chip. With many instructions available, the CWDSP1650 can also act as a system controller in its own right.

The CWDSP1650 is supported by a full suite of development tools. Support tools for source code and system-level development include:

- Assembler/Linker

- Optimizing C compiler

- Simulator

- On-Core Emulation Module (OCEM)

- Evaluation board

VHDL or Verilog models implement the top-down design methodology.

### **1.2 Features Summary**

This section summarizes the features of the CWDSP1650.

### 1.2.1 General Architecture

These features describe general items regarding the hardware architecture of the CWDSP1650:

- Modified Harvard Architecture

- Single-cycle multiply/accumulate instructions

- 36-bit Arithmetic Logical Unit (ALU) and barrel shifter

- Four 36-bit accumulators

- Saturation mode on overflow

- Single-cycle exponent evaluation

- Double-precision multiplication support

- Bit field operations

- Four-level zero-overhead nested looping (interruptible)

- Repeat instruction (interruptible)

- Four user interrupts available (three maskable, one nonmaskable)

- In-circuit debugging support, with on-chip emulator (OCEM)

- Automatic context switching with shadow registers

- Software stack support

- Six 16-bit data pointers for X-data memory and Y-data memory with three additional alternative registers

- Support for direct, indirect, index, and modulo addressing modes

- Off-core X-memory and Y-memory facilitating modular design

- Automatic boot procedure support (self and host booting)

### 1.2.2 Memory Organization

These features describe the memory support of the CWDSP1650.

- 64 Kword addressable data space

- 64 Kword addressable program memory space

- Off-core data memory: up to 64 Kwords for X-memory, and up to 32 Kwords for Y-memory

### 1.2.3 Physical Technology

These features summarize the physical attributes and technology of the CWDSP1650 DSP core:

- ◆ 0.35-micron G10<sup>™</sup> technology

- Fully static design

- ♦ 3.3 V ±10% operation

- Core Power 2.0 mW/MHz

- Core Size 5.0 mm<sup>2</sup>

### 1.2.4 Instruction Set Summary

Table 1.1 summarizes the instruction set for the core. All instructions are 16 bits long, and most execute in a single cycle. Several instructions including ADDV, SUBV, CMPV, and PUSH can optionally have a long immediate operand (due to the long immediate operand, these instructions are executed in two cycles.)

| Ор         | Description                                | Ор         | Description                                                |

|------------|--------------------------------------------|------------|------------------------------------------------------------|

| Arithmetic | and Logical Instructions                   | BMU Instr  | uctions                                                    |

| ADD        | Add                                        | SET        | Set Bit-field                                              |

| SUB        | Subtract                                   | RST        | Reset Bit-field                                            |

| OR         | Logical OR                                 | CHNG       | Change Bit-field                                           |

| AND        | Logical AND                                | TST0       | Test Bit-Field for Zeros                                   |

| XOR        | Logical Exclusive OR                       | TST1       | Test Bit-Field for Ones                                    |

| CMP        | Compare                                    | TSTB       | Test Specific Bit                                          |

| ADDL       | Add to Low Accumulator                     | SHFC       | Shift Accumulators According to Shift Value                |

| SUBL       | Subtract from Low Accumulator              |            | Register Conditionally                                     |

| ADDH       | Add to High Accumulator                    | SHFI       | Shift Accumulators by an Immediate Shift Value             |

| SUBH       | Subtract from High Accumulator             | EXP        | Evaluate the Exponent Value                                |

| CMPU       | Compare Unsigned                           | MODB       | Modify Bx-Accumulator Conditionally                        |

| ADDV       | Add Long Immediate Value <sup>1</sup>      | MODB I     | Modifications:                                             |

| SUBV       | Subtract Long Immediate Value <sup>1</sup> | SHR        | Shift Right                                                |

| CMPV       | Compare Long Immediate Value <sup>1</sup>  | SHR4       | Shift Right Four                                           |

| NORM       | Normalize                                  | SHL        | Shift Left                                                 |

| DIVS       | Division Step                              | SHL4       | Shift Left Four                                            |

| MAX        | Maximum between Two Ax-Accumulators        | ROR        | Rotate Right through Carry                                 |

| MAXD       | Maximum between Data Memory Location       | ROL        | Rotate Left through Carry                                  |

|            | and Ax-Accumulator                         | CLR        | Clear                                                      |

| MIN        | Minimum between Two Ax-Accumulators        | Move Inst  | ructions                                                   |

| LIM        | Limit Ax-Accumulator                       | MOV        | Move Data                                                  |

| MODA       | Modify Ax-Accumulator Conditionally        | MOVP       | Move from Program Memory into Data Memory                  |

| MODA I     | Modifications:                             | MOVD       | Move from Data Memory into Program Memory                  |

| SHR        | Shift Right                                | MOVS       | Move and Shift according to Shift Value Register           |

| SHR4       | Shift Right Four                           | MOVSI      | Move and Shift according to an Immediate Shift Value       |